ZPUC: A New Configuration of Single DC Source for Modular Multilevel Converter Applications

Saeed Arazm, Kamal Al-Haddad

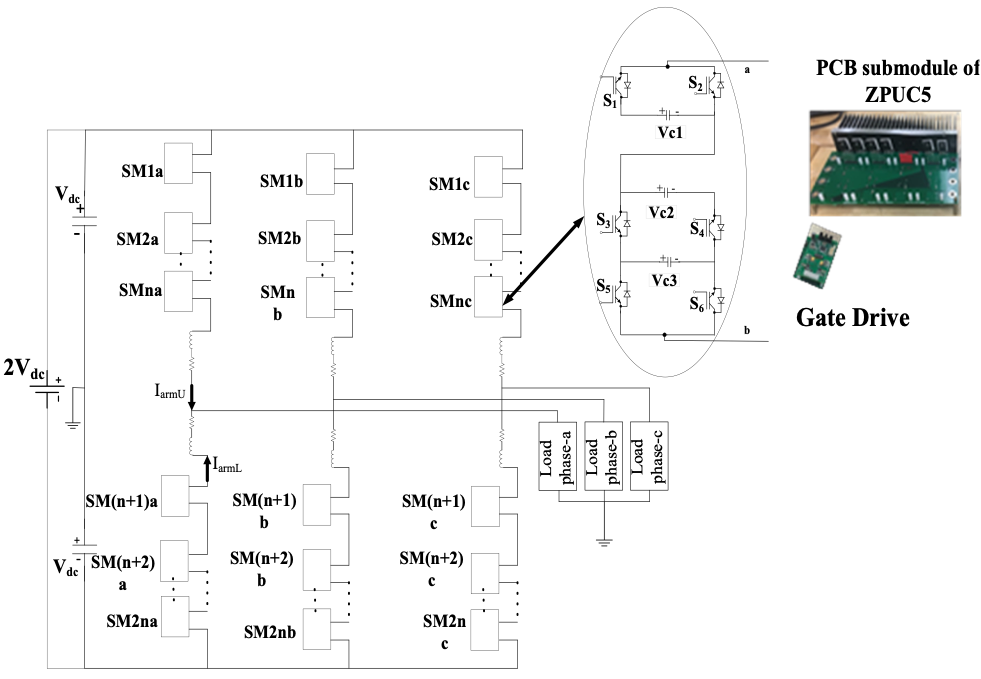

ABSTRACT: Z packed U-cell (ZPUC) converter topology is presented in this paper as a new type of multilevel converter topology that can be operated in a single phase as well as in three-phase configurations while using a single DC source. Since each U-cell includes two switches which operates complimentarily and one capacitor, in this topology, three U-cells are needed to generate 5 or 7 voltage levels. Moreover, the proposed configuration for the ZPUC is more appropriate for high-power application modular multilevel converters (MMCs) to increase the voltage levels compared to other topologies.

ZPUC generates unipolar waveform which is highly functional on MMC application to generate higher voltage levels compared to bipolar topologies such as (packed U-cells) PUC and full-bridge (FB). However, it requires DC fault circuit breaker for disconnecting of DC fault current. Moreover, the components count of ZPUC are less than half of the half-bridge (HB) unipolar topology. The remarkable note is that the DC voltage source on ZPUC is divided among the submodules of leg (one phase), while it is divided among the submodules of the arm on the other topologies. This solution reduces the cost, weight, and volume of the ZPUC converter compared to its counterpart converters with a similar power rating. Furthermore, this new structure offers lower power loss and higher reliability to generate equivalent number of voltage levels.

Accurate voltage balancing on small-sized auxiliary capacitors is due to integrated modulation strategy without using additional controllers; additionally, the reduction of total harmonic distortion (THD) in AC currents for higher voltage levels is an advantage of this configuration. A full topology sequence of operation and performance analysis of ZPUC based on the 5-L inverter is investigated in Matlab-Simulink and experimentally validated on a 3 kVA prototype. The obtained results illustrate the good dynamic performance of the proposed topology and the implemented integrated switching pattern voltage balancing.